## CPE/EE 422/522 Advanced Logic Design L07

Electrical and Computer Engineering University of Alabama in Huntsville

## **Outline**

- What we know

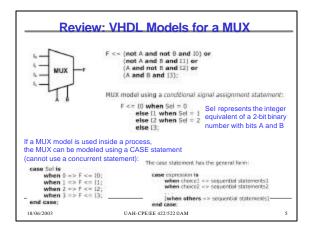

- How to model Combinational Networks in VHDL

- · Structural, Dataflow, Behavioral

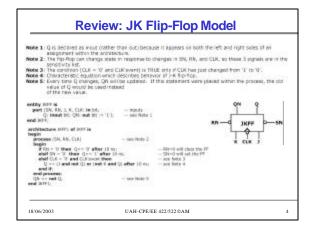

- How to model Flip-flops in VHDL

- Processes

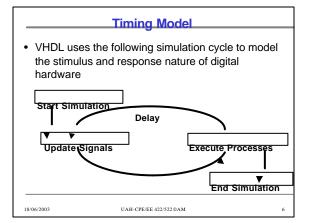

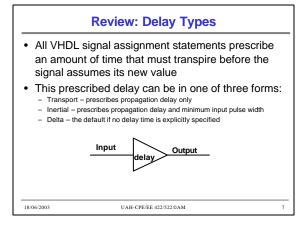

- Delays (delta, transport, inertial)

- · What we do not know

- How to model FSM in VHDL

- Wait statements

- Variables, Signals, Arrays

- VHDL Operators

- Procedures, Functions

- Packages, Libraries

- Additional Topics (if time)

8/06/2003 UAH-CPE/EE 422/522 ©AM

# Review: VHDL Program Structure Entity Architecture Entity Architecture Entity Architecture Module 1 Entity Architecture Module 2 Entity Architecture Module 1 Entity Architecture Architecture Architectu

```

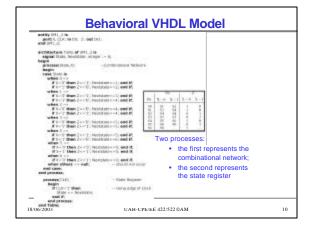

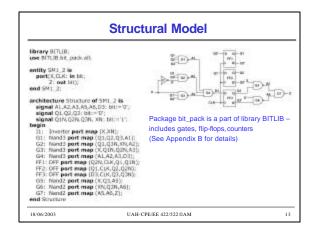

- The fallening is a description of the seguaritial machinu of - Figure 1-17 in terms of its read states equations.

The fallening state insignment was used:

- 500 ->0; 53 ->4; 52 ->5; 53 ->7; 54 ->6; 55 ->3; 56 ->2

entity SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Country SPL 2 is perfix CLC in bit:

- Count

```

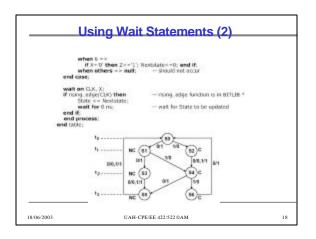

## **Wait Statements**

- ... an alternative to a sensitivity list

- Note: a process cannot have both wait statement(s) and a sensitivity list

- Generic form of a process with wait statement(s)

process

begin

sequential - statements

wait statement

sequential - statements

wait-statement

...

end process;

- How wait statements work?

- Execute seq. statement until a wait statement is encountered.

- Wait until the specified condition is satisfied.

- Then execute the next set of sequential statements until the next wait statement is encountered.

- When the end of the process is reached start over again at the beginning.

18/06/2003 UAH-CPE/EE 422/522@AM

## **Forms of Wait Statements**

wait on sensitivity-list;

wait for time-expression;

wait until boolean-expression;

- Wait on

- until one of the signals in the sensitivity list changes

- Wait for

- waits until the time specified by the time expression has elapsed

- What is this: wait for 0 ns;

- Wait until

- the boolean expression is evaluated whenever one of the signals in the expression changes, and the process continues execution when the expression evaluates to TRUE

18/06/2003 UAH-CPE/EE 422/522 ©AM 16

##

## **Variables**

- What are they for: Local storage in processes, procedures, and functions

- · Declaring variables

```

variable list_of_variable_names : type_name

[ := initial value ];

```

- Variables must be declared within the process in which they are used and are local to the process

- Note: exception to this is SHARED variables

18/06/2003 UAH-CPE/EE 422/522 ©AM

## **Signals**

- · Signals must be declared outside a process

- Declaration form

```

signal list_of_signal_names : type_name

[ := initial value ];

```

Declared in an architecture can be used anywhere within that architecture

/06/2003 UAH-CPE/EE 422/522 ©AM

## **Constants**

· Declaration form

```

constant constant_name : type_name := constant_value;

constant delay1 : time := 5 ns;

```

- Constants declared at the start of an architecture can be used anywhere within that architecture

- Constants declared within a process are local to that process

18/06/2003 UAH-CPE/EE 422/522 ©AM 21

## Variables vs. Signals

· Variable assignment statement

variable\_name := expression;

- expression is evaluated and the variable is instantaneously updated (no delay, not even delta delay)

- · Signal assignment statement

```

signal_name <= expression [after delay];</pre>

```

expression is evaluated and the signal is scheduled to change after delay; if no delay is specified the signal is scheduled to be updated after a delta delay

18/06/2003 UAH-CPE/EE 422/522 ©AM 22

## Variables vs. Signals (cont'd)

```

Process Using Variables

eatify durinty is

eatify durinty is

eatify durinty is

signal trigger, sark; afteger = 0,

begin

process

variable var2: integer = 1;

variable var2: integer = 2;

variable var2:

```

18/06/2003 UAH-CPE/EE 422/522 ©AM

## Predefined VHDL Types

- Variables, signals, and constants can have any one of the predefined VHDL types or they can have a user-defined type

- Predefined Types

- bit {'0', '1'}

- boolean {TRUE, FALSE}

- integer [-2<sup>31</sup> 1.. 2<sup>31</sup> 1}

- real floating point number in range -1.0E38 to +1.0E38

- character legal VHDL characters including loweruppercase letters, digits, special characters, ...

- time an integer with units fs, ps, ns, us, ms, sec, min,

## **User Defined Type**

Common user-defined type is <u>enumerated</u>

```

type state_type is (S0, S1, S2, S3, S4, S5);

signal state : state_type := S1;

```

- If no initialization, the default initialization is the leftmost element in the enumeration list (S0 in this example)

- VHDL is strongly typed language => signals and variables of different types cannot be mixed in the same assignment statement, and no automatic type conversion is performed

18/06/2003

UAH-CPE/EE 422/522 ©AM

## **Arrays**

Example

```

type SHORT_WORD is array (15 downto 0) of bit;

signal DATA_WORD : SHORT_WORD;

variable ALT_WORD : SHORT_WORD := "01010101010101011";

constant ONE_WORD : SHORT_WORD := (others => '1');

```

- ALT\_WORD(0) rightmost bit

- ALT\_WORD(5 downto 0) low order 6 bits

- · General form

## Arrays (cont'd)

· Multidimensional arrays

```

type matrix4x3 is array (1 to 4, 1 to 3) of integer;

variable matrixA: matrix4x3 :=

((1,2,3), (4,5,6), (7,8,9), (10,11,12));

```

- matrixA(3, 2) = ?

- · Unconstrained array type

type intvec is array (natural range<>) of integer;

type matrix is array (natural range<>).natural range<>)

of integer;

· range must be specified when the array object is declared

## Sequential Machine Model Using State Table

## Predefined Unconstrained Array Types

Bit\_vector, string

type bit\_vector is array {natural range <>>} of bit;

type string is array {positive range <>>} of character;

constant string: string(i to 29) := "This string is 29 characters."|

constant A : bit\_vector(0 to 5) := "10101";

-- ('1', '0', '1', '0', '1');

- Subtypes

- include a subset of the values specified by the type

subtype SHORT\_WORD is: bit\_vector(15 to 0);

- POSITIVE, NATURAL predefined subtypes of type integer

18/06/2003 UAH-CPE/EE 422/522@AM 29

## VHDL Operators

- 1. Binary logical operators: and or nand nor xor xnor

- 2. Relational: = /= < <= > >=

- 3. Shift: sll srl sla sra rol ror

- 4. Adding: + & (concatenation)

- 5. Unary sign: + -

- 6. Multiplying: \* / mod rem

- 7. Miscellaneous: not abs \*\*

- Class 7 has the highest precedence (applied first), followed by class 6, then class 5, etc

## **Example of VHDL Operators**

```

In the following expression, A, B, C, and D are bit_vectors:

(A & not B or C roe 2 and D) = "110010"

The operators would be applied in the order:

not, B, ror, or, and, =

If A = "110", B = "111", C = "011000", and D = "111011", the computation would proceed as follows:

not B = "000" (bit-by-bit complement)

A B not B = "110000" (concatenation)

C roe 2 = "000110" (retain right 2 places)

(A & not B) or C roe 2) = "1101010" (bit-by-bit or)

(A & not B) or C roe 2) and D = "110010" [bit-by-bit and)

[(A S not B) or C roe 2) and D = "110010"] = TRUE

(the parentheses force the equality test to be done last and the result is TRUE)

```

UAH-CPE/EE 422/522 @AM

31

## **Example of Shift Operators**

```

The shift operators can be applied to any bit_vector or boolean_vector. In the following examples, A is a bit_vector equal to "10010101":

A shi 2 is "01010100" [shift left logical, filled with "0"]

A shi 3 is "00010010" [shift right logical, filled with "0"]

A sha 3 is "10101111" [shift left arithmetic, filled with right bit)

A sha 3 is "10101100" [shift right arithmetic, filled with left bit)

A not 3 is "10101100" (rotate left)

A not 5 is "10101100" (rotate right)

IN06/2003

UAH-CREEE 422/522@AM

3.2

```

## **VHDL Functions**

Functions execute a sequential algorithm and return a single value to calling program

```

function rotate_night (reg: bit_wactor)

return bit_wector is

begin

return reg rer 1;

end rotate_night;

```

A = "10010101"

B <- rotate right(A);</li>

General form

function function-name (formal-parameter-list)

return return-type is

[declarations]

begin

sequential statements -- must include return return-value;

end function-name;

18/06/2003 UAH-CPE/EE 422/522@AM

## For Loops

```

General form of a for loop:

[loop-label:] for loop-index in range loop

sequential statements

end loop [loop-label]; Exit statement has the form:

exit; — or

exit when condition;

For Loop Example:

-- cargain book B-character strings and return TRUE if equal

function comp. string(string1, string2: string(1 to 8))

return booken is

variable B: boolean;

begin

loopes; for j in 1 to 8 loop

8 i = string1(j) = string2(j);

exit when S=FALSE;

end loop bopes;

return b;

end comp. string;

loopes | string2(j);

end comp. string;

loopes | string3(j);

end comp. string;

loopes | string3(j);

end comp. string;

loopes | string3(j);

end loop string;

loopes | string3(j);

loopes | string

```

### Add Function

```

- This function adds 2 4-bit vectors and a carry.

- It returns a 5-bit sum

function adds 4,8 bit, vector(3 downto 0); carry; bit)

return bit, vector is

variable cout; bit;

variable cout; bit; vector(4 downto 0):="00000";

begin

loopt: for i in 0 to 3 loop

cut := (A(i) and B(i)) or (A(i) and cin) or (B(i) and cin);

Sum(i):= A(i) xor B(i) xor cin;

cn loop loopt;

Sum(4):= cout;

return Sum;

end add4;

Example function call;

```

Sum1 <= add4(A1, B1, cin);

### VHDL Procedures

- Facilitate decomposition of VHDL code into modules

- Procedures can return any number of values using output parameters

- · General form

```

procedure procedure_name (formal-parameter-list) is

[declarations]

begin

Sequential-statements

end procedure_name;

procedure_name (actual-parameter-list);

```

## Procedure for Adding Bit\_vectors -- This procedure adds two n-bit bit, vectors and a carry and -- returns an n-bit sum and a carry. Addi and Add2 are assumed -- to be of the same length and dimensioned n-1 downto 0. procedure Addxec (Add1, Add2: in bit, vector; Chr. in bit, signal Sum: out bit vector; signal Court: out bit; finit paskive) is variable C(bit; begin C(r) Cin; for i in 0 to n-1 loop -- Sum(i) -- Add2(i) xer Add2(i) xer C; C(r) -- (Add2(i) and Add2(i)) or (Add1(i) and C) or (Add2(i) and C); end loop; Cot x =- C; end Addvec; Example procedure calt: Addvec(Al, Bi, Cin, Sum1, Cout, 4);

### **Parameters for Subprogram Calls** Actual Parameter Mode Class Procedure Call Function Call constant? expression expression signal signal signal variable variable n/a out/inout signal signal n/a variable3 variable n/a 1 default mode for functions 2 default for in mode 3 default for out/input mode UAH-CPE/EE 422/522 ©AM 38

## Provide a convenient way of referencing frequently used functions and components Package declaration package package-name is package declarations end [package][package-name]; Package body [optional] package body gectarations end [package body declarations end [package body][package name];

**Packages and Libraries**

```

Library BITLIB — bit_pack package

package is pack is

included a 1942 in 1942

```

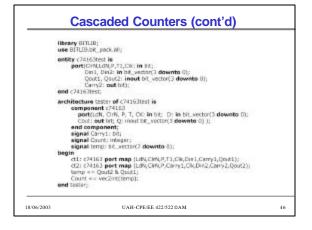

## VHDL Model for a 74163 Counter

- 74613 4-bit fully synchronous binary counter

- · Counter operations

| Control Signals |     |     | Next State |          |         |     |                   |

|-----------------|-----|-----|------------|----------|---------|-----|-------------------|

| Cirt            | LdN | P+T | Q3*        | Q2*      | Q1*     | 001 |                   |

| 0               | ×   | ×   | 0          | 0        | 0       | 0   | (clear)           |

| 1               | 0   | ×   | D3         | D2       | D1      | 00. | (parallel load)   |

| 1               | 1   | 0   | - Q3       | Q2       | Q1      | Q0  | (no change)       |

| 1               | 1   | 1   |            | resent : | state + | 1   | (increment count) |

- Generate a Cout in state 15 if T=1

- Cout =  $Q_3Q_2Q_1Q_0T$

18/06/2003 UAH-CPE/EE 422/522 ©AM

```

VHDL Model for a 74163 Counter

- 74163 FILLY SYNCHRONOUS COUNTER

Strary CITLIS:

- contains vir2vec and vec2sit functions

use BTULES is

- pertitute, park as;

entity (74163 is

- pertitute, priv, r, r, occ as bit; G: lie bit, vector(3 downto 0);

count out bit; Q: liesus bit, vector(3 downto 0);

count cust bit; Q: liesus bit, vector(3 downto 0);

count cust bit; Q: liesus bit, vector(3 downto 0);

count cust bit; Q: liesus bit, vector(3 downto 0);

count cust bit; Q: liesus bit, vector(3 downto 0);

count cust bit; Q: liesus bit, vector(3 downto 0);

count cust bit; Q: liesus bit, vector(3 downto 0);

count cust bit; Q: liesus bit, vector(3 downto 0);

count cust bit; Q: liesus bit, vector(3 downto 0);

count cust bit; Q: liesus bit, vector(3 downto 0);

count cust bit; Q: liesus bit, vector(3 downto 0);

count cust bit; Q: liesus bit; Q: liesus

```

# Cascaded Counters Out 1 Out 2 Out 1 Out 1 Out 2 Out 1 Out 1 Out 2 Out 1 Out 1 Out 1 Out 2 Out 1 Out 2 Out 1 Out 2 Out 2 Out 1 Out 2 Out 2 Out 1 Out 2 Out

# Additional Topics in VHDI Attributes Transport and Inertial Delays Operator Overloading Multivalued Logic and Signal Resolution IEEE 1164 Standard Logic Generics Generate Statements Synthesis of VHDL Code Synthesis Examples Files and Text IO INFORMATION ACCEPTETE 422/522 BAM 47

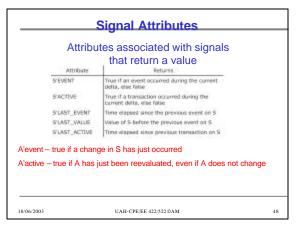

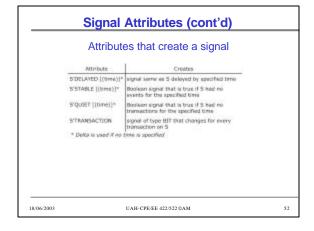

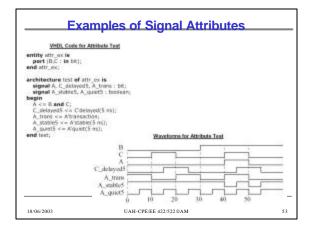

## Signal Attributes (cont'd)

- Event

- occurs on a signal every time it is changed

- Transaction

- occurs on a signal every time it is evaluated

- · Example:

```

A <= B \, - \, B changes at time T

```

|        | A'event | B'event |

|--------|---------|---------|

| Т      |         |         |

| T + 1d |         |         |

18/06/2003 UAH-CPE/EE 422/522 ©AM 49

### Signal Attributes (cont'd) entity test is if (A'event) then Aev := '1'; end; else Aev := '0'; end if; architecture bmtest of test is if (A'active) then Aac := '1'; else Aac := '0'; signal A : bit; signal B : bit; end if; signal C : bit; end if; if (B'event) then Bev := '1'; else Bev := '0'; end if; begin A <= not A after 20 ns; if (B'active) then Bac := '1'; else Bac := '0'; end if; if (C'event) then Cev := '1'; else Cev := '0'; C <= A and B; process(A, B, C) variable Aev : bit; variable Aac : bit; variable Bev : bit; variable Bac : bit; end if; if (C'active) then Cac := 'l'; else Cac := '0'; end if; variable Cev : bit; variable Cac : bit; UAH-CPE/EE 422/522 ©AM 50

### Signal Attributes (cont'd) /test/a /test/line 15/bev delta /test/b /test/line\_\_15/bac /test/c /test/line\_\_15/cev /test/line\_\_15/aev /test/line\_\_15/cac /test/line\_\_15/aac 0 0 0 0 0 0 +0 0 0 0 0 0 1 0 0 0 1 1 0 1 0 +1 20 +0 1 1 0 1 1 20 +1 1 1 1 0 0 0 0 1 1 40 +0 0 1 1 1 1 0 0 0 0 40 +1 0 1 0 0 0 0 0 1 1 UAH-CPE/EE 422/522 ©AM 51

```

check: process

begin

wait until rising_edge(Clk);

assert (D'stable(setup_time))

report("Setup time violation")

severity error;

wait for hold_time;

assert (D'stable(hold_time))

report("Hold time violation")

severity error;

end process check;

```

### **Array Attributes** Type ROM is erroy (0 to 15, 7 downto 0) of bit; Signal ROM1 : ROM; ALEFT(N) left bound of 6th ROMI'LEFT(1) = 0 ROMI'LEFT(2) = 7 light bound of Nth edgs range OML'RIGHT(1) = 15OML'RIGHT(2) = 0ANDGRINI largest bound of lith Index range OM1'HIGH(1) = 15 OM1'HIGH(2) = 7 ALOW(N) smallest bound of Mth index range 041.FOM(1) = 0 041.FOM(1) = 0 ATRANGE(N) ith index range OMI:RANGE(1) = 0 to 15 OMI:RANGE(2) = 7 downto 0 IOMITREVENSE\_RANGE(1) = 15 downs 0 IOMITREVERSE\_RANGE(2) = 0 to 7 AREVERSE RANCEINI Mith Implex nongel reversed ROMITLENGTH(1) = 16 ROMITLENGTH(2) = 6 A can be either an array name or an array type Array attributes work with signals

```

Recap: Adding Vectors

- This procedure adds two n-bit bit, vectors and a carry and neturns an infoit sum and a Carry. Add1 and Add2 are assumed to be of the same length and themsolved n-1 downto d.

procedure Adds vec

[Asst Add2 in the Vector]

[Add2 in the

```

# Procedure for Adding Bit Vectors - This procedure adds bno bit, vectors and a carry and returns a sam. - and a carry, Both bit, vectors about be of the same largets. procedure Addition(2 [Ideas, Add2] is Dit, vector() Cas is bit] signal Same out bit, vector() signal Court out bit, vector() signal Court out bit | sector() signal Court out bit) is versible to be : Cin, side of it is court of the process of the Add1; side of it is court of the Add2 length-1 downto () is Add1; side of it is court of Add2 length-1 downto () is Add1; side of it is extended, Same length of downto () is Sam; begin sesert ((n1) length = n2 length mast be equal ( serverse, range loag S(i) = n n(i) serverse, range loag S(i) = n n(i)

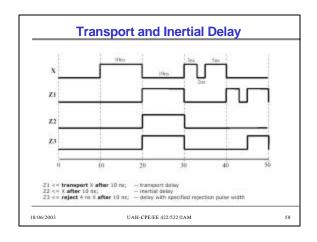

## Transport and Inertial Delay (cont'd) Z3 <= reject 4 ns X after 10 ns; Reject is equivalent to a combination of inertial and transport delay: Zm <= X after 4 ns; Z3 <= transport Zm after 6 ns; Statements executed at time T -B at T+1, C at T+2 A <= transport B after 1 ns; A <= transport C after 2 ns; Statements executed at time T Statements executed at time T -C at T + 1: -C at T + 2: A <= B after 1 ns; A <= transport B after 2 ns; $A \le C$ after 2 ns: A <= transport C after 1 ns;

## Operator Overloading

- · Operators +, operate on integers

- Write procedures for bit vector addition/subtraction

addvec, subvec

- Operator overloading allows using + operator to implicitly call an appropriate addition function

- How does it work?

- When compiler encounters a function declaration in which the function name is an operator enclosed in double quotes, the compiler treats the function as an operator overloading ("+")

- when a "+" operator is encountered, the compiler automatically checks the types of operands and calls appropriate functions

## **VHDL Package with Overloaded Operators**

```

** This package provides love overloaded functions for the plus operation gardings bit monitored in the plus operation gardings bit monitored in the post operation gardings bit monitored in the post operation function in 1,4401, Addit bit, sector insteam bit, vector; sector, each te, post-ood.

**Behavior STULID:

** use STULID: bit, pack add;

**packages body bit, post-odd is

** This Addition returns a bit, vector deam of two bit, vector operands.

**This Add is performed bit by bit with an internal carry function.

**This Addition returns a bit, vector insteam bit, vector is used to the vector in the post operands.

**This Addition returns a bit, vector insteam bit, vector is used to the vector in the ve

```

## **Overloaded Operators**

- A, B, C bit vectors

- $A \le B + C + 3$ ?

- A <= 3 + B + C?

- Overloading can also be applied to procedures and functions

- procedures have the same name –

type of the actual parameters in the procedure call determines which version of the procedure is called

8/06/2003 UAH-CPE/EE 422/522 ©AM 62

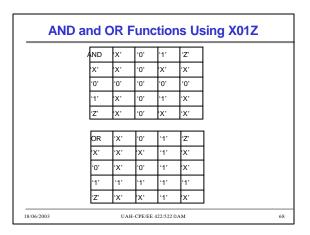

## **Multivalued Logic**

- Bit (0, 1)

- Tristate buffers and buses => high impedance state 'Z'

- · Unknown state 'X'

- e. g., a gate is driven by 'Z', output is unknown

- a signal is simultaneously driven by '0' and '1'

# Tristate Buffers use WORK Surpack all services and provided and provi

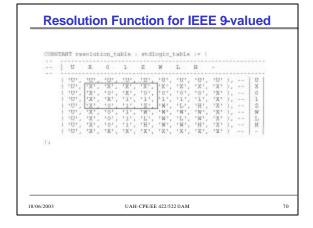

## Signal Resolution

- VHDL signals may either be resolved or unresolved

- Resolved signals have an associated resolution function

- Bit type is unresolved

- there is no resolution function

- if you drive a bit signal to two different values in two concurrent statements, the compiler will generate an error

18/06/2003 IJAH-CPE/EE 422/522@AM 65

##

##

### **IEEE 1164 Standard Logic** · 9-valued logic system - 'U' - Uninitialized - 'X' - Forcing Unknown - '0' - Forcing 0 If forcing and weak signal are - '1' - Forcing 1 tied together, the forcing signal - 'Z' - High impedance dominates. - 'W' - Weak unknown Useful in modeling the internal - 'L' - Weak 0 operation of certain types of ICs. - 'H' - Weak 1 - '-' - Don't care In this course we use a subset of the IEEE values: X10Z UAH-CPE/EE 422/522 ©AM

```

function 'and' (1: std_alogic; r: std_alogic) return UNDI is begin return (and '1: std_alogic; r: std_alogic) return UNDI is legin return (and '; std_alogic, exclor ) return std_logic_vector is alogic vector is alogic, vector (1: in RENOTH ) is () alogic vector is alogic vector (1: in RENOTH ) is () to return the result of the result of

```